Anche se i chiplet sono presenti da decenni, il loro uso è stato storicamente limitato ad applicazioni specifiche e specializzate. Oggi, tuttavia, sono all’avanguardia della tecnologia, alimentando milioni di PC desktop, workstation, server, console per videogiochi, telefoni e persino dispositivi indossabili in tutto il mondo.

Nel giro di pochi anni, la maggior parte dei principali produttori di chip ha adottato la tecnologia dei chiplet per guidare l’innovazione. È ormai chiaro che i chiplet sono destinati a diventare lo standard dell’industria. Esploriamo cosa li rende così significativi e come stanno plasmando il futuro della tecnologia.

TL;DR: Cosa sono i Chiplet?

I chiplet sono processori segmentati. Invece di consolidare ogni parte in un unico chip (approccio noto come monolitico), sezioni specifiche sono prodotte come chip separati. Questi chip individuali vengono poi montati insieme in un unico pacchetto utilizzando un sistema di connessione complesso.

Questo arrangiamento consente alle parti che possono beneficiare dei metodi di fabbricazione più recenti di essere ridotte in dimensioni, migliorando l’efficienza del processo e permettendo di inserire più componenti.

Le parti del chip che non possono essere ridotte significativamente o che non necessitano di riduzione possono essere prodotte utilizzando metodi più vecchi ed economici.

Sebbene il processo di produzione di tali processori sia complesso, il costo complessivo è tipicamente inferiore. Inoltre, offre alle aziende di processori un percorso più gestibile per espandere la loro gamma di prodotti.

Scienza del Silicio

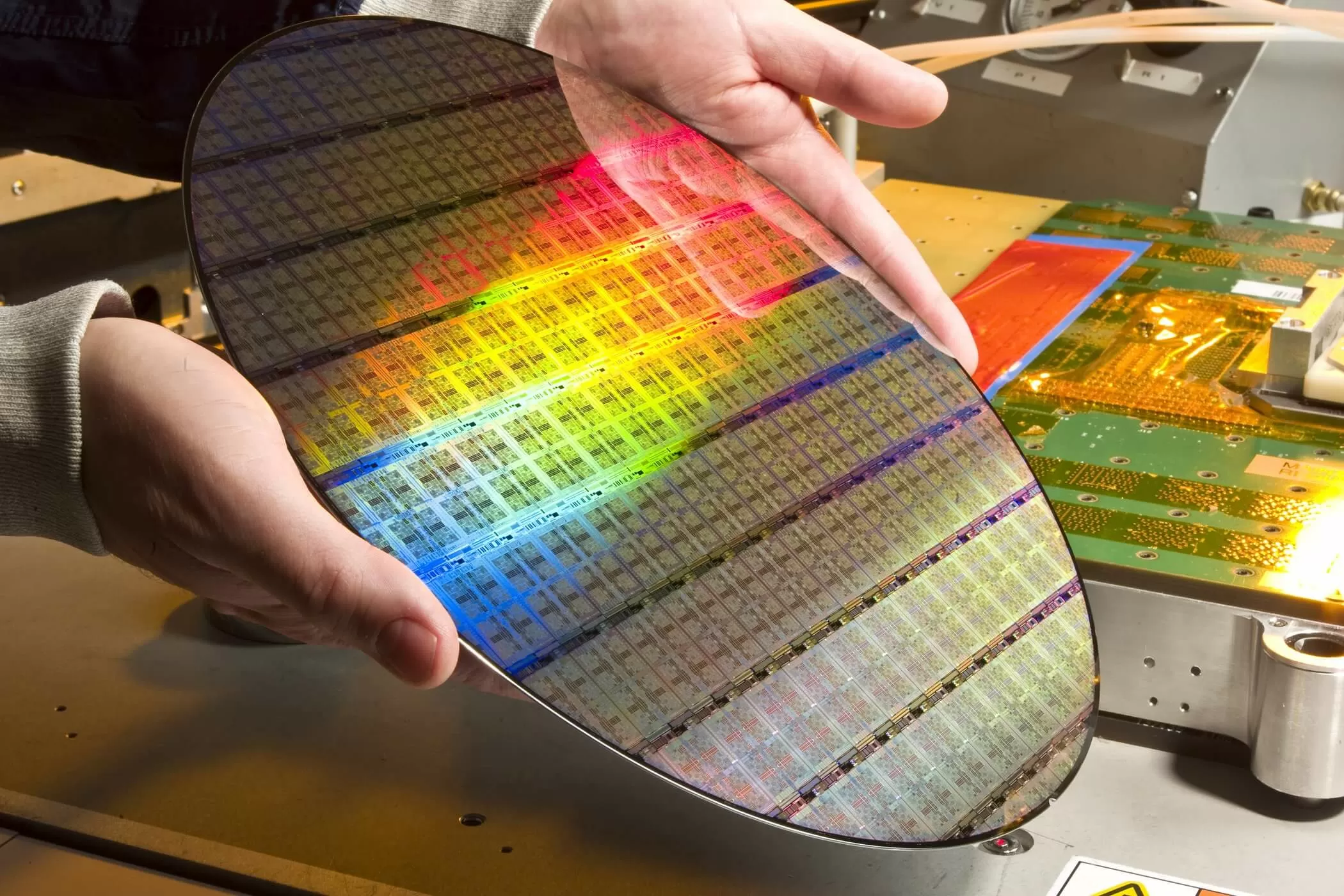

Per comprendere appieno perché i produttori di processori si sono rivolti ai chiplet, dobbiamo prima esplorare come questi dispositivi vengono realizzati. CPU e GPU iniziano la loro vita come grandi dischi di silicio ultra-puro, tipicamente poco meno di 12 pollici (300 mm) di diametro e 0,04 pollici (1 mm) di spessore.

Questo wafer di silicio subisce una serie di passaggi intricati, risultando in più strati di materiali diversi – isolanti, dielettrici e metalli. I pattern di questi strati sono creati attraverso un processo chiamato fotolitografia, dove la luce ultravioletta è proiettata attraverso una versione ingrandita del pattern (una maschera), e successivamente ridotta tramite lenti alla dimensione richiesta.

Il pattern viene ripetuto, a intervalli prestabiliti, sulla superficie del wafer e ciascuno di essi diventerà alla fine un processore. Poiché i chip sono rettangolari e i wafer sono circolari, i pattern devono sovrapporsi al perimetro del disco. Queste parti sovrapposte vengono ultimate scartate poiché non funzionali.

Una volta completato, il wafer viene testato utilizzando una sonda applicata a ogni chip. I risultati dell’esame elettrico informano gli ingegneri sulla qualità del processore rispetto a una lunga lista di criteri. Questa fase iniziale, nota come selezione dei chip, aiuta a determinare il “grado” del processore.

Ad esempio, se il chip è destinato a essere una CPU, ogni parte dovrebbe funzionare correttamente, operando entro un intervallo specifico di velocità di clock a una tensione specifica. Ogni sezione del wafer viene poi categorizzata in base a questi risultati di test.

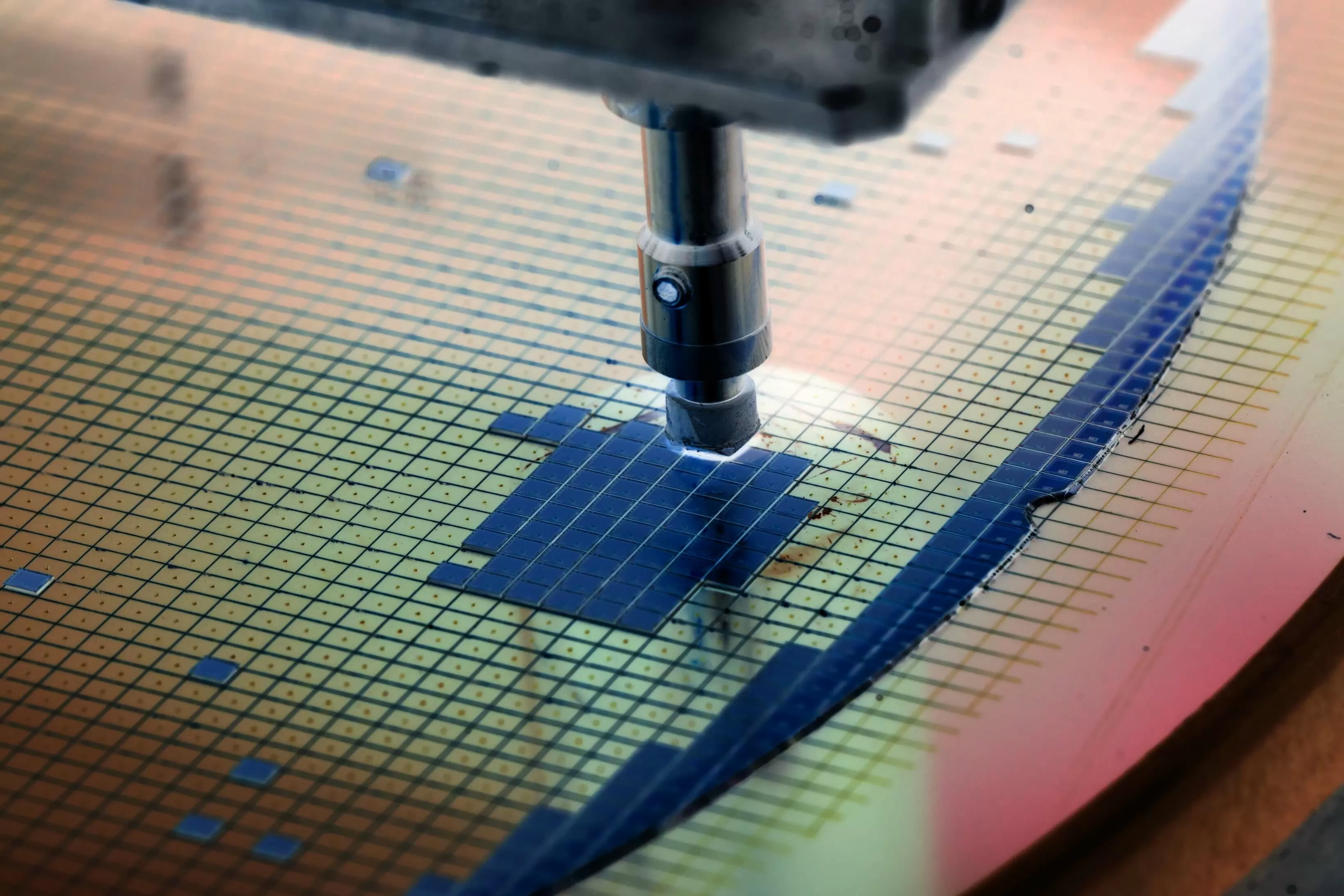

Alla fine, il wafer viene tagliato in pezzi individuali, o “dies,” che sono utilizzabili. Questi dies vengono poi montati su un substrato, simile a una scheda madre specializzata. Il processore subisce ulteriori imballaggi (ad esempio, con uno spreader di calore) prima di essere pronto per la distribuzione.

L’intera sequenza può richiedere settimane di produzione e aziende come TSMC e Samsung addebitano tariffe elevate per ogni wafer, tra i 3.000 e i 20.000 dollari a seconda del nodo di processo utilizzato.

“Nodo di processo” è il termine usato per descrivere l’intero sistema di fabbricazione. Storicamente, erano nominati dopo la lunghezza del gate del transistor. Tuttavia, con il miglioramento della tecnologia di produzione e la possibilità di realizzare componenti sempre più piccoli, la nomenclatura non ha più seguito alcun aspetto fisico del die ed ora è semplicemente uno strumento di marketing.

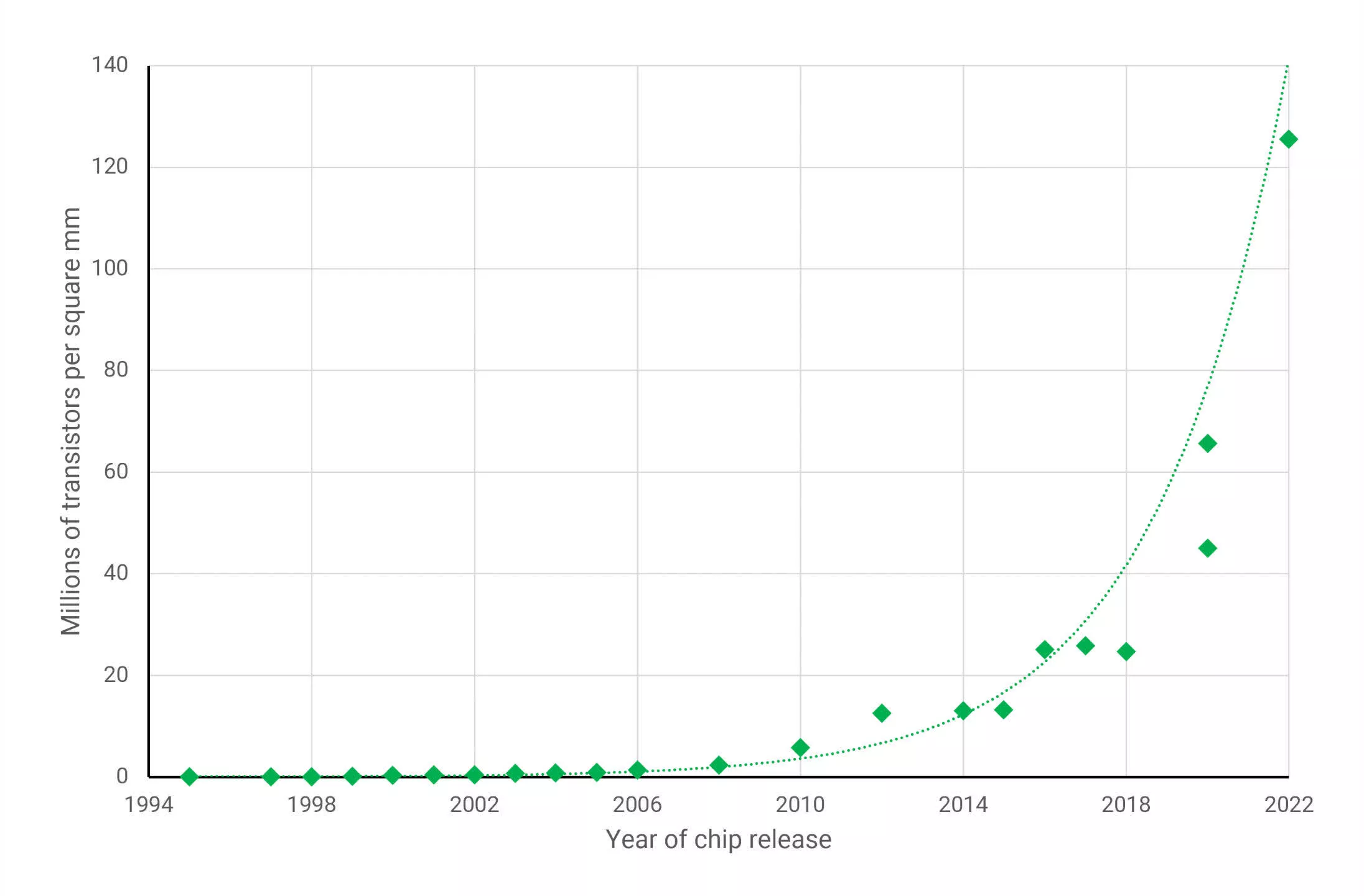

Tuttavia, ogni nuovo nodo di processo porta vantaggi rispetto al suo predecessore. Potrebbe essere più economico da produrre, consumare meno energia alla stessa velocità di clock (o viceversa), o avere una densità più elevata. Quest’ultimo parametro misura quanti componenti possono essere inseriti in un’area di die data. Nel grafico qui sotto, puoi vedere come questo è evoluto nel corso degli anni per le GPU (i chip più grandi e complessi che troverai in un PC)…

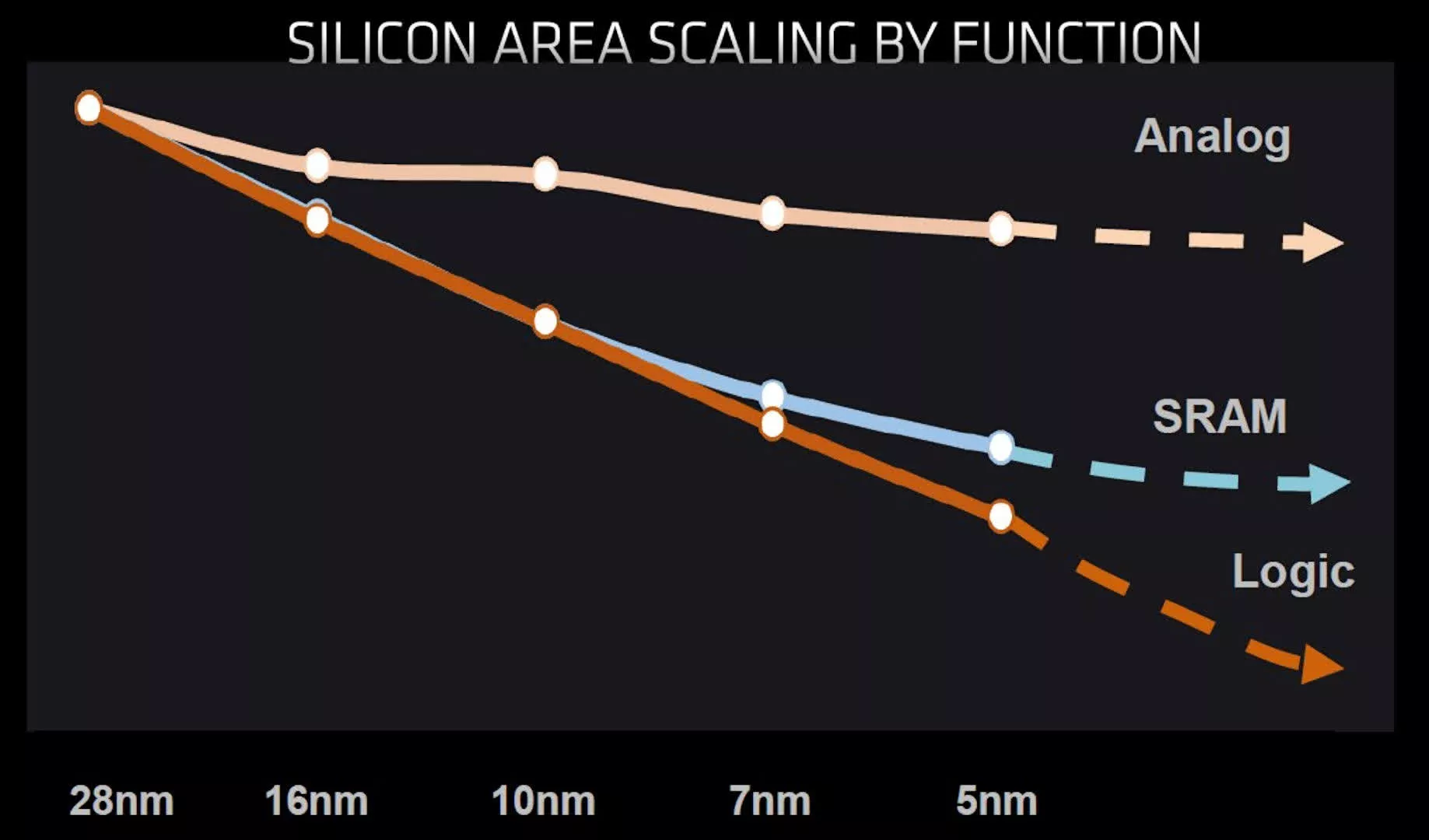

I miglioramenti nei nodi di processo offrono ai tecnici un modo per aumentare le capacità e le prestazioni dei loro prodotti, senza dover utilizzare chip grandi e costosi. Tuttavia, il grafico sopra citato racconta solo parte della storia, poiché non ogni aspetto di un processore può trarre vantaggio da questi avanzamenti.

I circuiti all’interno dei chip possono essere allocati in una delle seguenti categorie ampie:

- Logica – gestisce dati, matematica e decisioni

- Memoria – di solito SRAM, che memorizza dati per la logica

- Analogico – circuiti che gestiscono i segnali tra il chip e altri dispositivi

Sfortunatamente, mentre i circuiti logici continuano a ridursi con ogni grande passo avanti nella tecnologia dei nodi di processo, i circuiti analogici sono cambiati poco e anche l’SRAM sta iniziando a raggiungere un limite.

Mentre la logica costituisce ancora la maggior parte del die, la quantità di SRAM nelle CPU e GPU odierne è cresciuta significativamente negli ultimi anni. Ad esempio, il chip Vega 20 di AMD utilizzato nella sua scheda grafica Radeon VII (2019), presentava un totale combinato di 5 MB di cache L1 e L2. Solo due generazioni di GPU dopo, il chip Navi 21 che alimenta la serie Radeon RX 6000 (2020), includeva oltre 130 MB di cache combinata – un notevole aumento di 25 volte.

Possiamo aspettarci che queste continuino ad aumentare con le nuove generazioni di processori, ma con la memoria che non scala verso il basso così bene come la logica, diventerà sempre meno conveniente produrre tutta la circuiteria sullo stesso nodo di processo.

In un mondo ideale, si progetterebbe un die dove le sezioni analogiche sono fabbricate sul nodo più grande ed economico, le parti SRAM su uno molto più piccolo, e la logica riservata alla tecnologia all’avanguardia assoluta. Purtroppo, questo non è praticamente realizzabile. Tuttavia, esiste un approccio alternativo.

Dividere e Conquistare

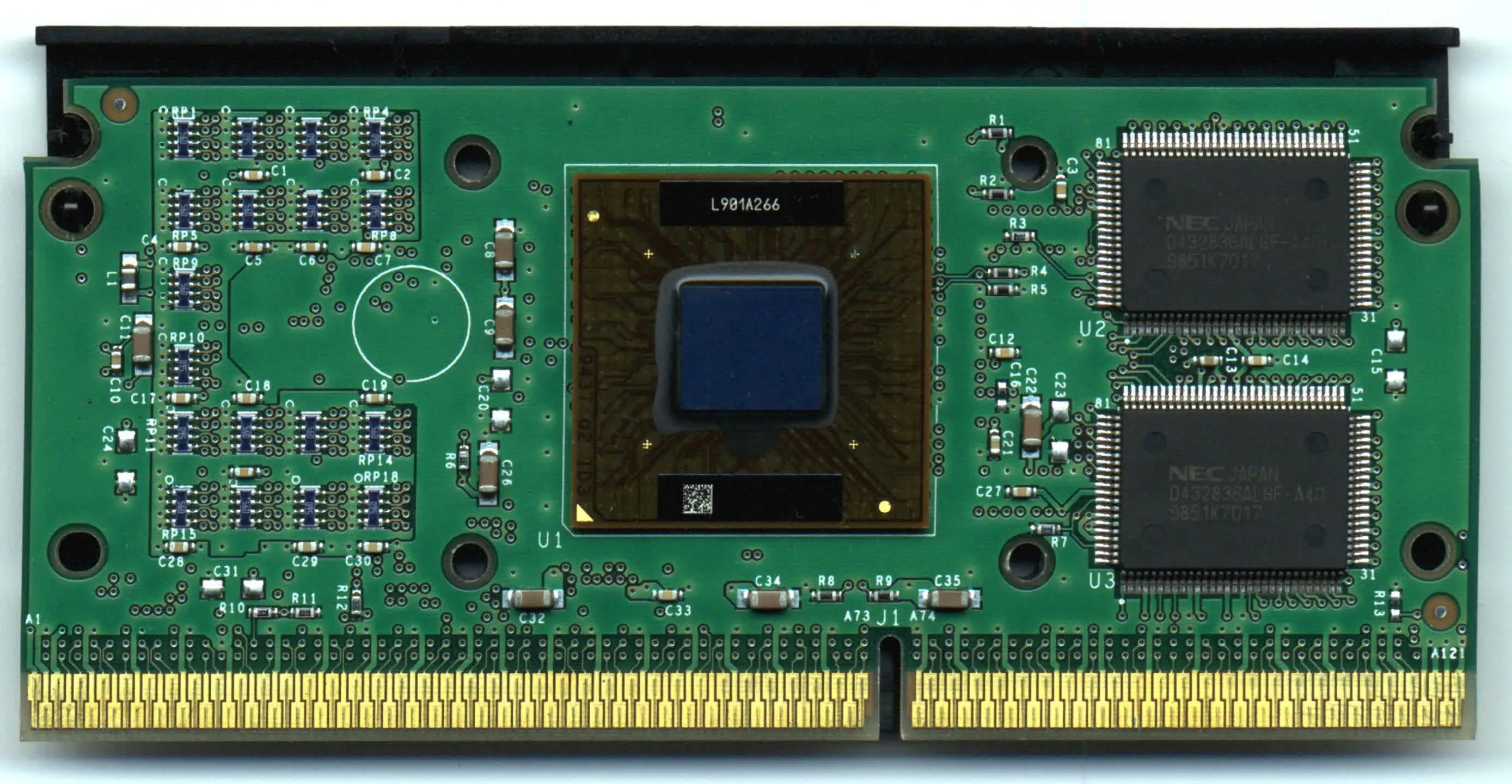

Nel 1995, Intel introdusse il Pentium II, successore del suo originale processore P5. Ciò che lo distingueva dagli altri processori dell’epoca era il design nascosto sotto il suo scudo di plastica: una scheda circuitale che ospitava due chip. Il chip principale conteneva tutta la logica di elaborazione e i sistemi analogici, mentre uno o due moduli SRAM separati fungevano da cache di Livello 2.

Mentre Intel produceva il chip principale, la cache veniva fornita da fornitori esterni. Questo approccio divenne abbastanza standard per i PC desktop dalla metà alla fine degli anni ’90, fino a quando i progressi nella fabbricazione dei semiconduttori permisero di integrare completamente logica, memoria e sistemi analogici in un unico die.

Mentre Intel continuava a sperimentare con più chip nello stesso pacchetto, si atteneva in gran parte all’approccio cosiddetto monolitico per i processori – cioè un chip per tutto. Per la maggior parte dei processori, non c’era bisogno di più di un die, poiché le tecniche di fabbricazione erano competenti (e accessibili) a sufficienza per mantenere tutto semplice.

Tuttavia, altre aziende erano più interessate a seguire un approccio multi-chip, in particolare IBM. Nel 2004, era possibile acquistare una versione a 8 chip della CPU server POWER4 che comprendeva quattro processori e quattro moduli di cache, tutti montati all’interno dello stesso corpo (noto come approccio multi-chip module o MCM).

Intorno a questo periodo, il termine “integrazione eterogenea” iniziò a comparire, in parte a causa dei lavori di ricerca svolti da DARPA. L’integrazione eterogenea mira a separare le varie sezioni di un sistema di elaborazione, fabbricarle individualmente sui nodi più adatti per ciascuna, e poi combinarle nello stesso pacchetto.

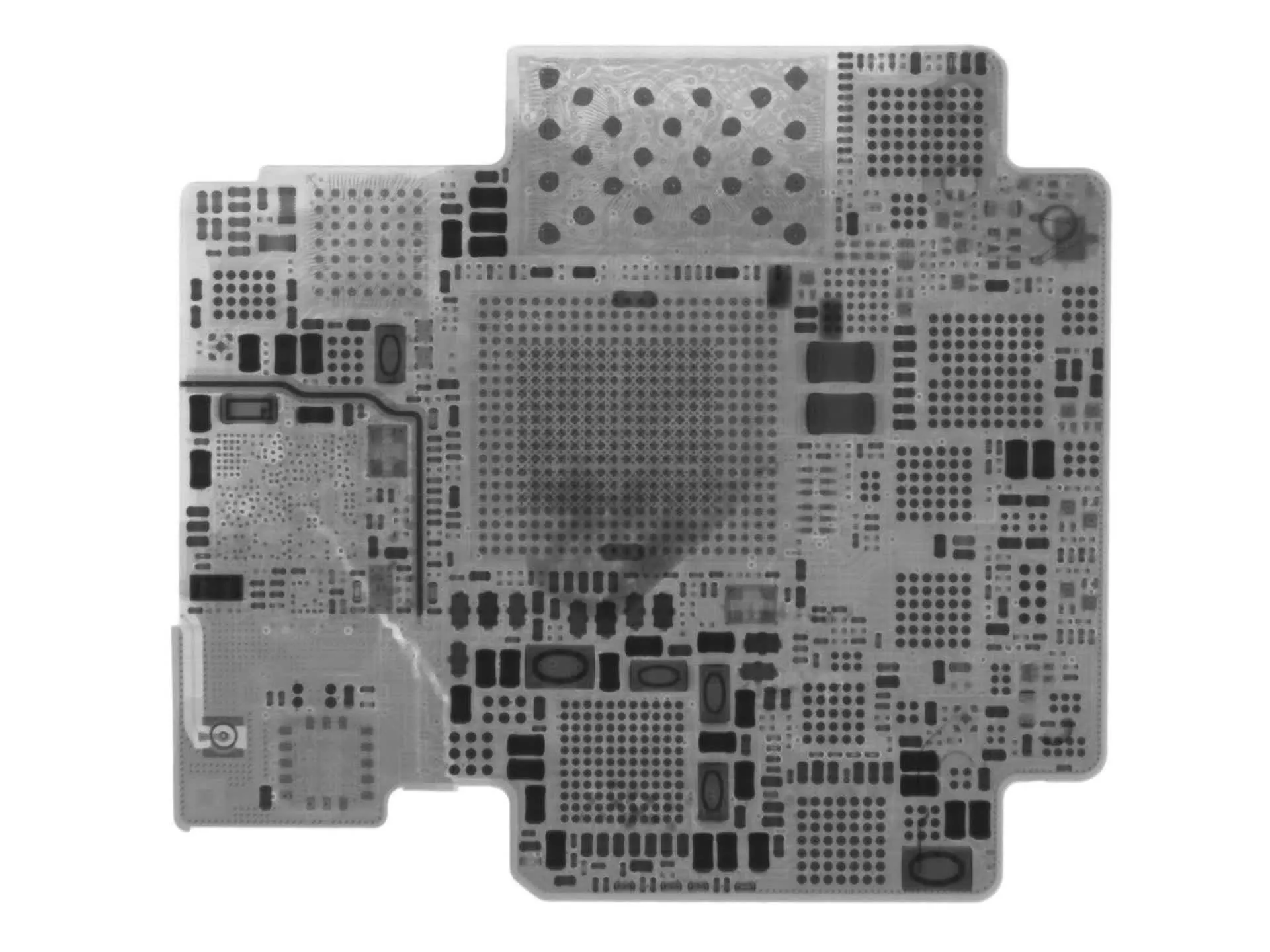

Oggi, questo è meglio conosciuto come system-in-package (SiP) ed è stato il metodo standard per equipaggiare gli smartwatch con chip fin dalla loro nascita. Ad esempio, l’Apple Watch Serie 1 ospita una CPU, un po’ di DRAM e NAND Flash, più controller multipli e altri componenti all’interno di una singola struttura.

Una configurazione simile può essere ottenuta avendo diversi sistemi tutti su un unico die (noto come SoC o system-on-a-chip). Tuttavia, questo approccio non permette di sfruttare i diversi prezzi dei nodi, né ogni componente può essere prodotto in questo modo.

Per un fornitore di tecnologia, utilizzare l’integrazione eterogenea per un prodotto di nicchia è una cosa, ma impiegarla per la maggior parte del proprio portafoglio è un’altra. Questo è esattamente ciò che ha fatto AMD con la sua gamma di processori. Nel 2017, il gigante dei semiconduttori ha introdotto la sua architettura Zen con il lancio della CPU desktop Ryzen a singolo die. Solo pochi mesi dopo, AMD ha debuttato con due linee di prodotti multi-chip: Threadripper ed EPYC, quest’ultima con configurazioni fino a quattro dies.

Con il lancio di Zen 2 due anni dopo, AMD ha pienamente abbracciato HI, MCM, SiP – chiamatelo come volete. Hanno spostato la maggior parte dei sistemi analogici fuori dal processore e li hanno collocati in un die separato. Questi sono stati prodotti su un nodo di processo più semplice ed economico, mentre uno più avanzato è stato utilizzato per la logica e la cache rimanenti.

E così, chiplet è diventata la parola d’ordine preferita.

Più piccolo è Meglio

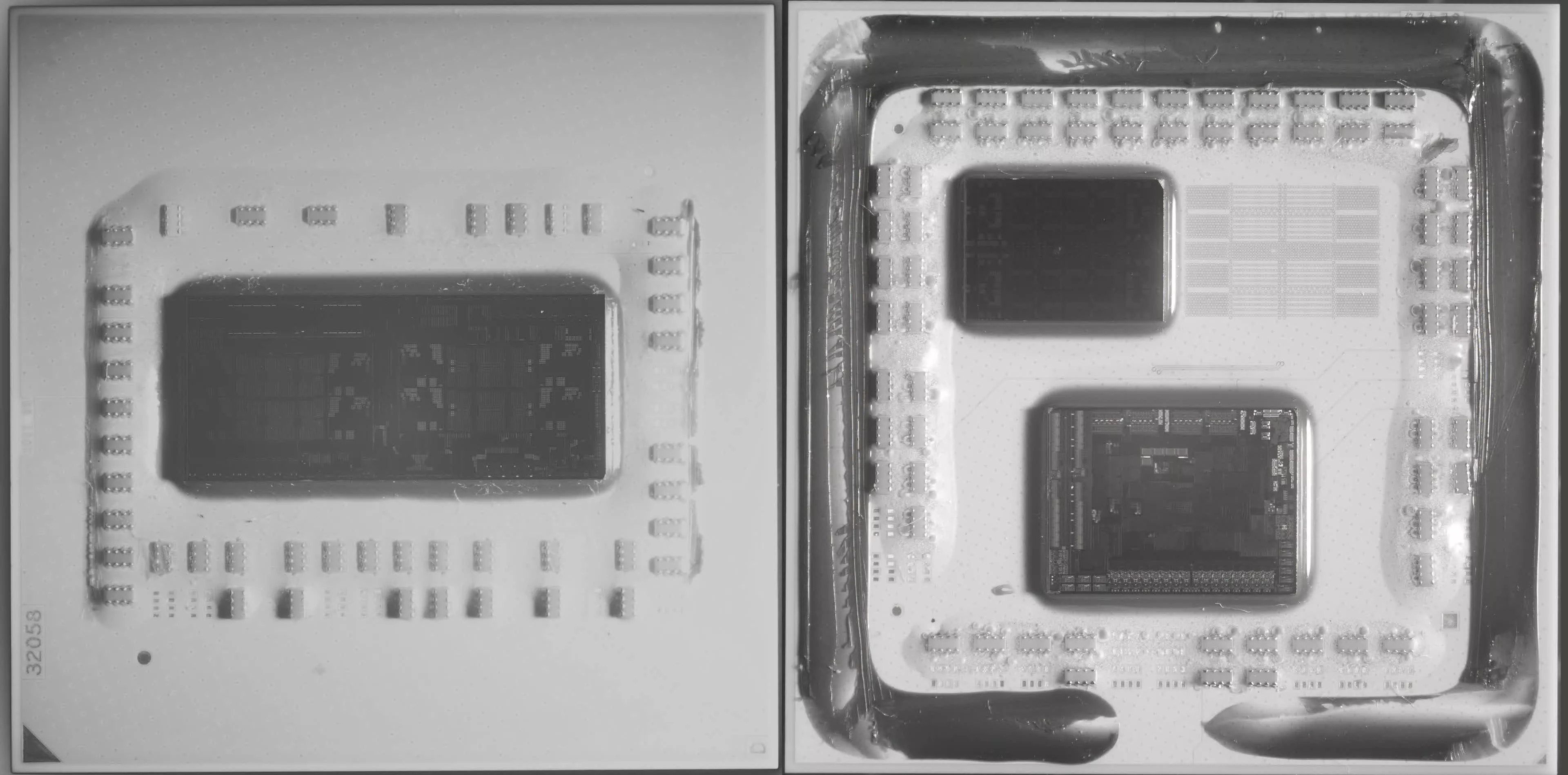

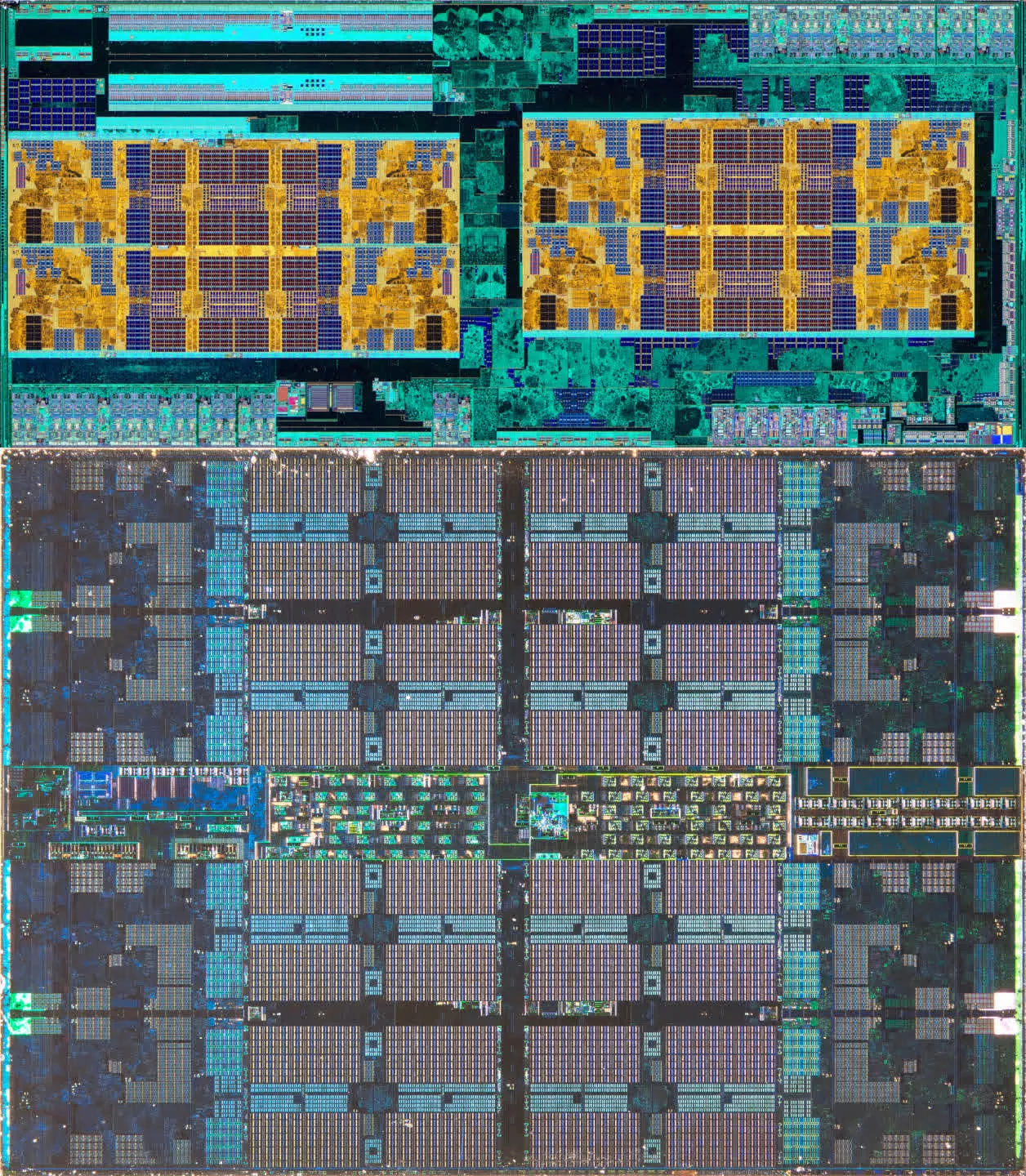

Per capire esattamente perché AMD ha scelto questa direzione, esaminiamo l’immagine qui sotto. Mostra due vecchie CPU della serie Ryzen 5: la 2600 a sinistra, che impiega l’architettura cosiddetta Zen+, e la 3600 a destra, alimentata da Zen 2.

I dissipatori di calore su entrambi i modelli sono stati rimossi, e le fotografie sono state scattate usando una telecamera a infrarossi. Il singolo die della 2600 ospita otto core, anche se due di essi sono disabilitati per questo particolare modello.

Questo è anche il caso della 3600, ma qui possiamo vedere che ci sono due dies nel pacchetto: il Core Complex Die (CCD) in alto, che ospita i core e la cache, e il Die di Input/Output (IOD) in basso, che contiene tutti i controller (per memoria, PCI Express, USB, ecc.) e le interfacce fisiche.

Poiché entrambe le CPU Ryzen si adattano allo stesso socket della scheda madre, le due immagini sono essenzialmente in scala. In superficie, potrebbe sembrare che i due dies nella 3600 abbiano un’area combinata più grande rispetto al singolo chip nella 2600, ma le apparenze possono ingannare.

Se confrontiamo direttamente i chip che contengono i core, è chiaro quanto spazio nel modello più vecchio sia occupato dai circuiti analogici – sono tutti i colori blu-verde che circondano i core dorati e la cache. Tuttavia, nel CCD Zen 2, pochissima area del die è dedicata ai sistemi analogici; è quasi interamente composto da logica e SRAM.

Il chip Zen+ ha un’area di 213 mm² ed è stato prodotto da GlobalFoundries utilizzando il suo nodo di processo 12nm. Per Zen 2, AMD ha mantenuto i servizi di GlobalFoundries per l’IOD da 125 mm² ma ha utilizzato il nodo N7 superiore di TSMC per il CCD da 73 mm².

L’area combinata dei chip nel modello più recente è più piccola, e vanta anche il doppio della cache L3, supportando una memoria più veloce e PCI Express. La parte migliore dell’approccio dei chiplet, tuttavia, è stata che le dimensioni compatte del CCD hanno reso possibile per AMD inserire un altro nel pacchetto. Questo sviluppo ha dato vita alla serie Ryzen 9, offrendo modelli da 12 e 16 core per i PC desktop.

Ancora meglio, utilizzando due chip più piccoli invece di uno grande, ogni wafer può potenzialmente produrre più dies. Nel caso del CCD Zen 2, un singolo wafer da 12 pollici (300 mm) può produrre fino all’85% in più di dies rispetto al modello Zen+.

Più piccolo è il pezzo che si prende da un wafer, meno probabile è trovare difetti di fabbricazione (poiché tendono ad essere distribuit

Messaggi simili:

- Intel adotterà il processo rivoluzionario 2nm di TSMC per i nuovi CPU Nova Lake!

- Intel Svela i Chip Panther Lake: Promette Prestazioni di Arrow Lake con Efficienza di Lunar Lake

- Produzione Imminente per i Chip 2nm di TSMC: iPhone 18 Pro tra i Primi a Utilizzarli!

- Imminente Lancio AMD Threadripper Pro 9000: Rivelazioni dai Log di Spedizione!

- Intel risponderà alla 3D V-Cache di AMD con Clearwater Forest legata al server, non con CPU desktop

Nicola Costanzo esplora il mondo della tecnologia e dell’innovazione. I suoi articoli illuminano le sfide digitali che plasmano il nostro futuro.